VHDL数控分频器编程

1、LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY speaker IS

PORT(clk:IN STD_LOGIC;

tone:IN STD_LOGIC_VECTOR (11 DOWNTO 0);

spk:OUT STD_LOGIC);

END ENTITY speaker;

ARCHITECTURE one OF speaker IS

SIGNAL preclk:STD_LOGIC;

SIGNAL fullspk:STD_LOGIC;

BEGIN

---------------------

divclk:PROCESS(clk)

VARIABLE Count8:STD_LOGIC_VECTOR (3 DOWNTO 0);

BEGIN

IF (clk'EVENT AND clk='1') THEN

IF Count8>7 THEN preclk<=NOT preclk;Count8:="0000";

ELSE Count8:=Count8+1;

END IF;

END IF;

END PROCESS divclk;

----------------------

genspk:PROCESS(preclk,tone)

VARIABLE Count12:STD_LOGIC_VECTOR(11 DOWNTO 0);

BEGIN

IF (preclk'EVENT AND preclk='1') THEN

IF Count12=16#FFF# THEN Count12:=tone;fullspk<='1';

ELSE Count12:=Count12+1;fullspk<='0';

END IF;

END IF;

END PROCESS genspk;

----------------------

delayspk:PROCESS (fullspk)

VARIABLE Count2:STD_LOGIC;

BEGIN

IF (fullspk'EVENT AND fullspk='1') THEN Count2:=NOT Count2;

IF Count2='1' THEN spk <='1';

ELSE spk<='0';

END IF;

END IF;

END PROCESS delayspk;

END ARCHITECTURE one;

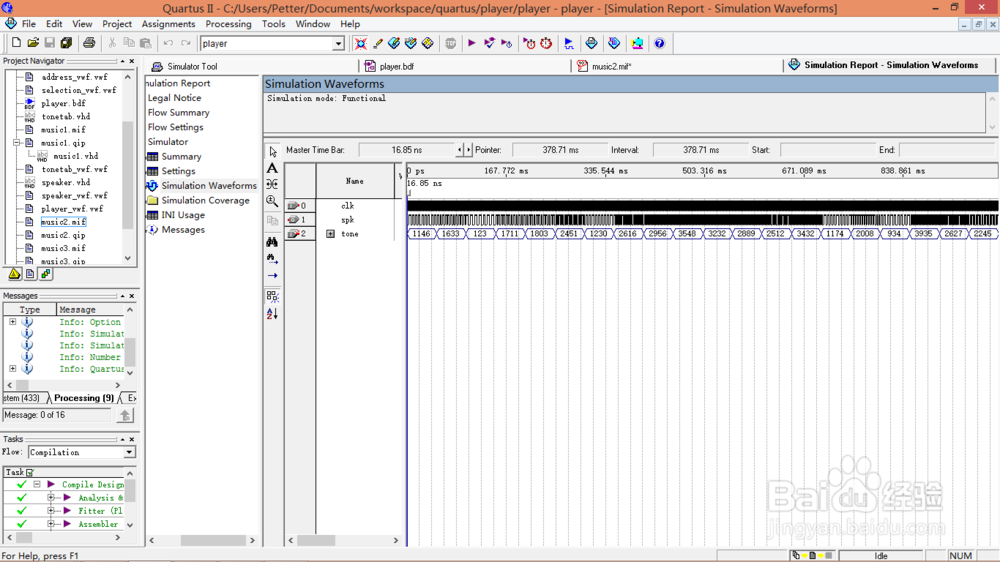

2、进行波形仿真

3、说明:

tone即是分频系数

spk既是产生的信号